最近はプリント基板も簡単に安く速く作れるようになり、ユニバーサル基板で作る手間を考えるとさっさと基板を作った方が良いと感じてきました。回路図とプリント基板のアートワーク作成にKiCadを使っています。どうせならKiCadで作った回路図から回路シミュレーションもできれば便利ですよね。KiCadにはNgspiceも組み込まれていますが、私はシミュレータとしてはLTspiceの方が使いやすいと感じています。しかし、シミュレーション用の回路図、基板作成用の回路図と別々に書くのは無駄なので、回路図は全てKiCadで書いて回路シミュレーションにも基板作成も共用できればと考えています。

以前の記事で、KiCadからLTspiceを使う手順を紹介しました。今回もその続きです。

今回は、半固定抵抗(VR)とbehaviorモデルについて紹介したいと思います。他にももっと良い(正しい)使い方があると思いますが、概要の紹介ということで…

私は、マニュアルを読んで使いこなすタイプではなく、とりあえずやってみるタイプなので、使えるようにしか使えません(笑)

Windows版のLTspiceがバージョン17から24にアップデートされ、LTspiceXVIIから LTspiceに名称も変更されたようです。デフォルトのインストールフォルダもLTCからADIに変わり、より使いやすく速くなっているそうです。なので、前回の記事からちょっとだけ設定変更が必要です。

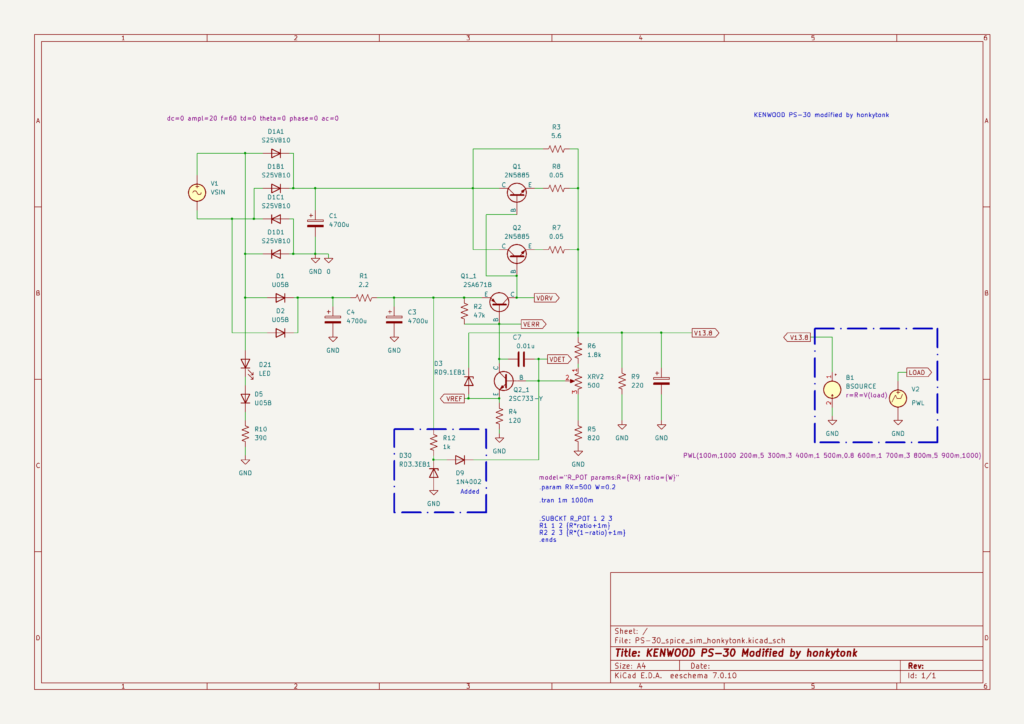

サンプルとして、以前 修理したTRIO/KENWOOD PS-30の回路図を使いたいと思います。

半固定抵抗(VR)を使う

電源には、電圧調整用のVRがついています。

このVRは、以下のようなサブサーキット(SUBCKT)で定義します。

|

1 2 3 4 |

.SUBCKT R_POT 1 2 3 R1 1 2 {R*ratio+1m} R2 2 3 {R*(1-ratio)+1m} .ends |

- SUBCKTの名称は、R_POT にしました。potentiometerの略です。他の名称でも構いません。

- ピンは、1, 2, 3の3本

2がスライダーのピンです。 - VR全体の抵抗値はR[Ω]

- ratioは、スライダーによって抵抗Rが分割される割合。

つまり、VRのスライダーがどこにあるか、50%の位置なら0.5, 80%の位置なら0.8 - R1は、ピン 1とピン2の間の抵抗R[Ω]にratioを掛けたもの、1mはratio = 0になった時に抵抗値が0[Ω]にならないように1[mΩ]を付けています。LTspiceでは、この1mは無くてもエラーにはなりませんが、Ngspiceでは0[Ω]はエラーになったと思います。

- R2は、ピン2と3の間の抵抗で、全体の抵抗R[Ω]からR1の分を引いたもの、1mの部分の説明はR1と同じです。

R1 + R2 ≒ R[Ω]になります。(正しくは、1mがあるので、R+2m[Ω])

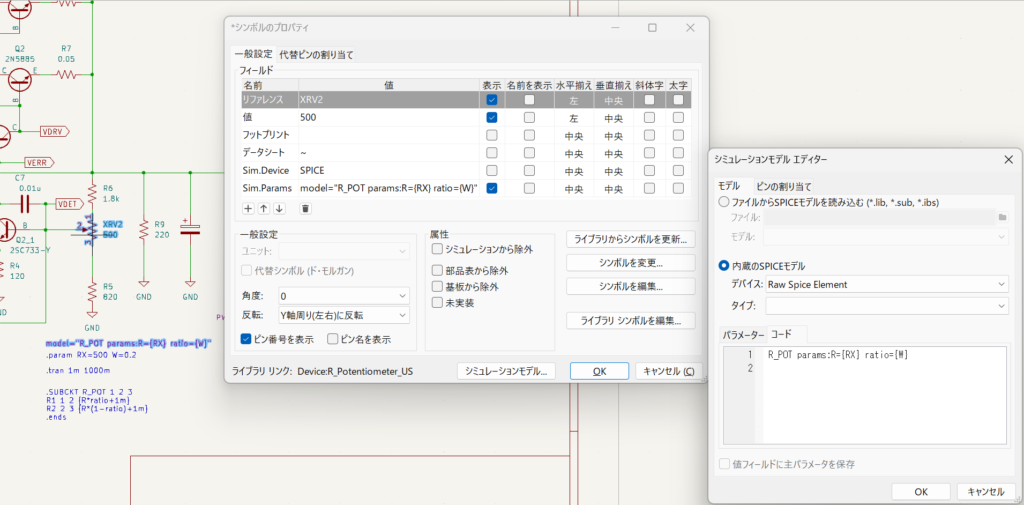

このR_POTを使うために、KiCadで以下のとおり設定します。

- VR(回路図では、XVR2)をクリックし、CTRL+Eでプロパティを開きます。

下の[シミュレーションモデル]を選択して、シミュレーション モデルエディターでmodel="R_POT params:R={RX} ratio={W}"と設定します。 - KiCadの「テキストを追加」で、VRの抵抗値とスライダーの位置(割合)を例えば、

.param RX=500 W=0.2と入力します。 (RXはXVR2の抵抗値、Wはスライダーの割合)

これが modelで指定した、Rとratioに代入されます。

負荷をつなぐ

電源をシミュレーションするには、負荷(ロード)が必要ですよね。

負荷として普通の抵抗を付けても良いですが、behaviorモデルを使ってみます。

behavivorモデルだけでシンプルにすることもできますが、今回はPWLと無理やり組み合わせてみました(笑)

- 2つの「V13.8」のラベルはお互いに接続されていることになります。

- そのV13.8に behaviorソース B1を負荷として接続します。

B1は抵抗のbehaviorモデルです。つまり、計算によって抵抗値を変化させることができます。 - 抵抗値を変化させるパラメータは、隣にあるV2です。V2はラベル「LOAD」に接続されています

- spiceでLOADの電圧を参照するにはV(load)と指定します。(LOADは大文字でも小文字でも同じです)

- つまり、

r=R=V(load)は、LOADの電圧を抵抗値Rにするということです。

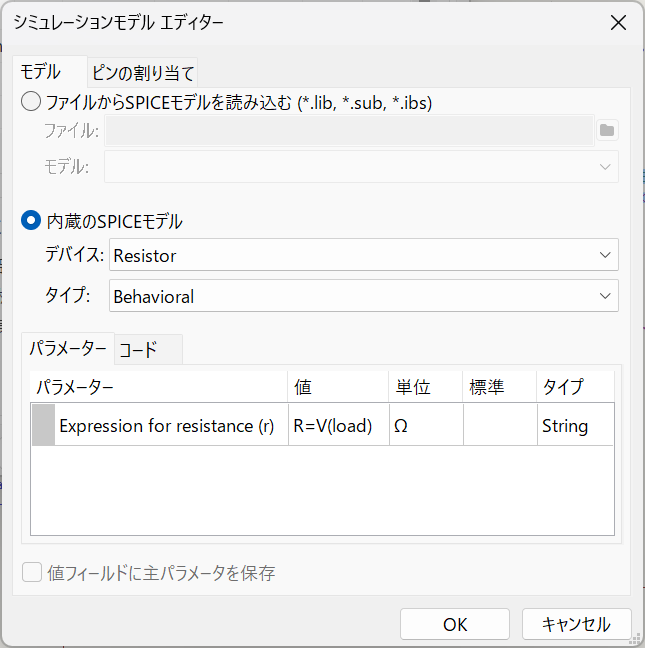

この例では、loadの電圧が1[V]の時Rは1[Ω]になります。KiCadでシミュレーションモデルを以下のように設定します。

- リファレンスはB1にしていますが、抵抗モデルなのでspiceではRB1になるようです。

- V2は、PWL(Piecewise Linear)で、時間と電圧をペアで並べて任意の(電圧)波形を作ります。

この例では、PWL(100m,1000 200m,5 300m,3 400m,1 500m,0.8 600m,1 700m,3 800m,5 900m,1000)としました。

100[ms]の時1000[V]、200[ms]の時5[V]、… とポイントで指定しています。ポイント間は直線で補間されます。 - こんな回りくどいことをしなくても、behaviorのパラメータに計算式を入れることでも代替可能です。

シミュレーションから除く部品、基板から除く部品の設定

基板には実装するけどシミュレーションは不要(or できない)な部品、 例えばLEDやコネクタ等や、逆にシミュレーションだけに使って基板には実装しないもの 、例えば電圧源等がありますよね。

これらの部品は、KiCadで部品のプロパティ(属性)を設定します。

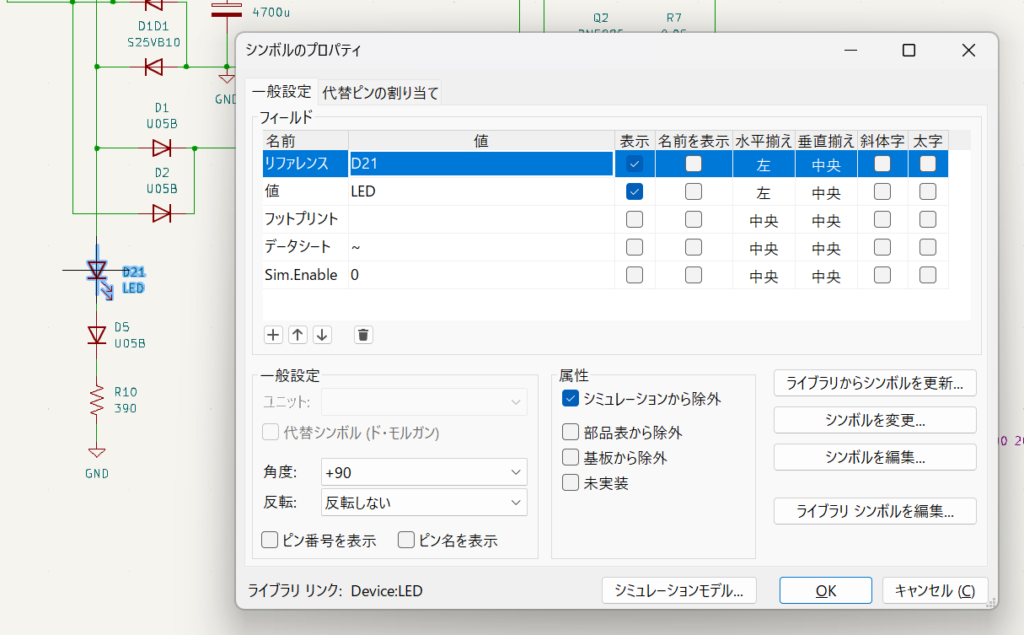

まずは、基板には実装するけど、シミュレーションはしなくて良い(点灯しているのは見えないし)部品 LEDの設定例です。

- LEDのシンボルをクリックして、CTRL+Eまたは、右クリックからプロパティを選択し、属性の「シミュレーションから除外」をチェックします。

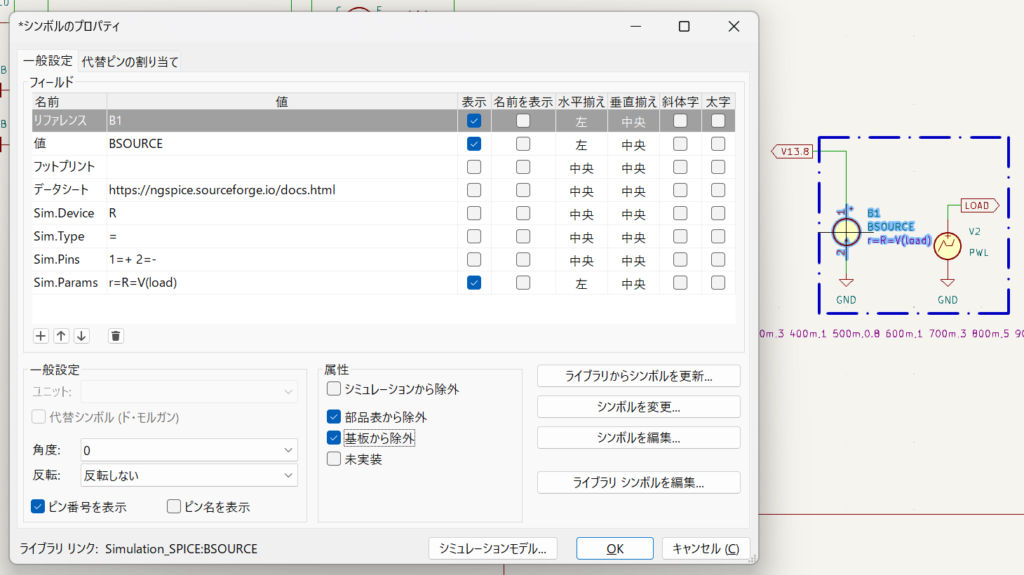

次は、シミュレーションには使うけど基板には実装しない(できない)部品の設定例です。

- behaviorモデルB1のシンボルをクリックして、CTRL+Eまたは、右クリックからプロパティを選択し、属性の「部品表から除外」、「基板から除外」をチェックします。

spiceディレクティブの設定

どのような条件でシミュレーショを実行するかを、spiceディレクティブ(指令)としてKiCadで設定する必要があります。「半固定抵抗(VR)を使う」の項で設定した .parameter もspiceディレクティブの一部です。.parameterは上で設定済なので、とりあえず過渡解析のコマンド .tran 1m 1000m を同様に「テキストを追加」で設定を追加します。

シミュレーションの実行

以前に紹介した手順と同じですが、LTspiceのバージョンアップに伴い、インストールディレクトリが変更になっています。

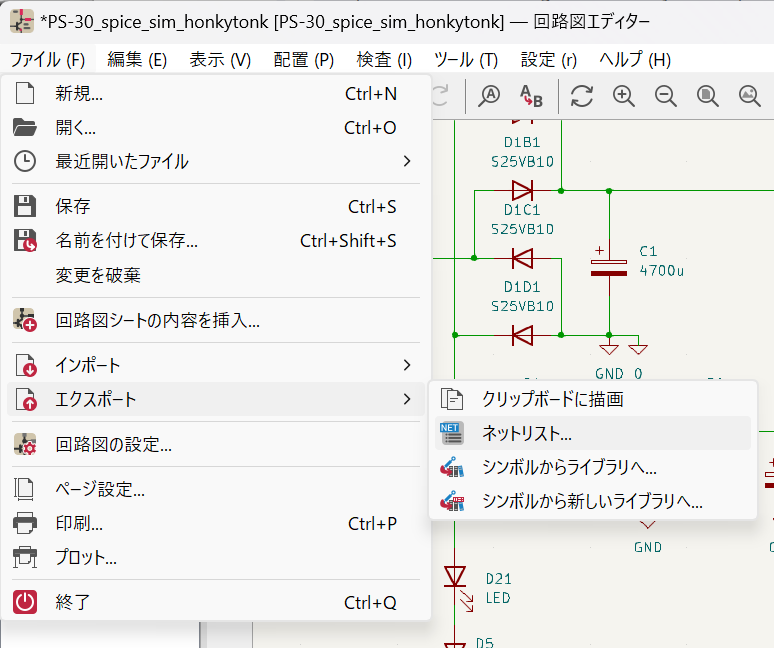

メニューから「ファイル」→「エクスポート」→ 「ネットリスト…」を選択します。

「ネットリストをエクスポート」の 「外部シミュレータのコマンド:」にLTspiceのパスを記入します。デフォルト設定でインストールした場合は、 C:\Program Files\ADI\LTspice\LTspice.exe です。

最後の “%I” 部分も必要です。消さないようにしましょう。

「ネットリストを作成してシミュレーターのコマンドを実行」を押すと、LTspiceが起動してシミュレーションが実行されます。

KiCadからLTspiceに直接回路図を渡すことはできないので、ネットリストとして渡すことになります。

ネットリストは次のようになりました。ダイオード、トランジスタはspiceの標準モデルを使っています。ツェナーダイオードのspiceモデルは、C:/Users/honkytonk/Documents/KiCad/spice/Models/Diode/zener.lib においています。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 |

.title KiCad schematic .include "C:/Users/honkytonk/Documents/KiCad/spice/Models/Diode/zener.lib" .model __D9 D .model __Q2_1 NPN .model __D1C1 D .model __D1B1 D .model __D1A1 D .model __D1 D .model __D2 D .model __D1D1 D .model __Q1_1 PNP .model __Q1 NPN .model __Q2 NPN .tran 1m 1000m .param RX=500 W=0.8 .SUBCKT R_POT 1 2 3 R1 1 2 {R*ratio} R2 2 3 {R*(1-ratio)} .ends R2 VERR Net-_Q1_1-E_ 47k C7 VERR VDET 0.01u XD3 VREF V13.8 DI_1N4739A XD30 0 Net-_D30-K_ DI_1N4728A D9 Net-_D30-K_ VDET __D9 R12 Net-_Q1_1-E_ Net-_D30-K_ 1k R4 0 VREF 120 Q2_1 VERR VDET VREF __Q2_1 C1 Net-_D1A1-K_ 0 4700u D1C1 0 Net-_D1B1-A_ __D1C1 D1B1 Net-_D1B1-A_ Net-_D1A1-K_ __D1B1 C3 Net-_Q1_1-E_ 0 4700u D1A1 Net-_D1-A_ Net-_D1A1-K_ __D1A1 V1 Net-_D1-A_ Net-_D1B1-A_ DC 0 SIN( 0 20 60 0 0 0 0 ) AC 0 R6 Net-_R6-Pad1_ V13.8 1.8k R9 0 V13.8 220 XRV2 Net-_R6-Pad1_ VDET Net-_R5-Pad2_ R_POT params:R={RX} ratio={W} R5 0 Net-_R5-Pad2_ 820 C5 V13.8 0 4700u V2 LOAD 0 PWL(100m,1000 200m,5 300m,3 400m,1 500m,0.8 600m,1 700m,3 800m,5 900m,1000) RB1 V13.8 0 R=V(load) R1 Net-_Q1_1-E_ Net-_D1-K_ 2.2 D1 Net-_D1-A_ Net-_D1-K_ __D1 D2 Net-_D1B1-A_ Net-_D1-K_ __D2 C4 Net-_D1-K_ 0 4700u D1D1 0 Net-_D1-A_ __D1D1 Q1_1 VDRV VERR Net-_Q1_1-E_ __Q1_1 Q1 Net-_D1A1-K_ VDRV Net-_Q1-E_ __Q1 R8 Net-_Q1-E_ V13.8 0.05 Q2 Net-_D1A1-K_ VDRV Net-_Q2-E_ __Q2 R7 Net-_Q2-E_ V13.8 0.05 .end |

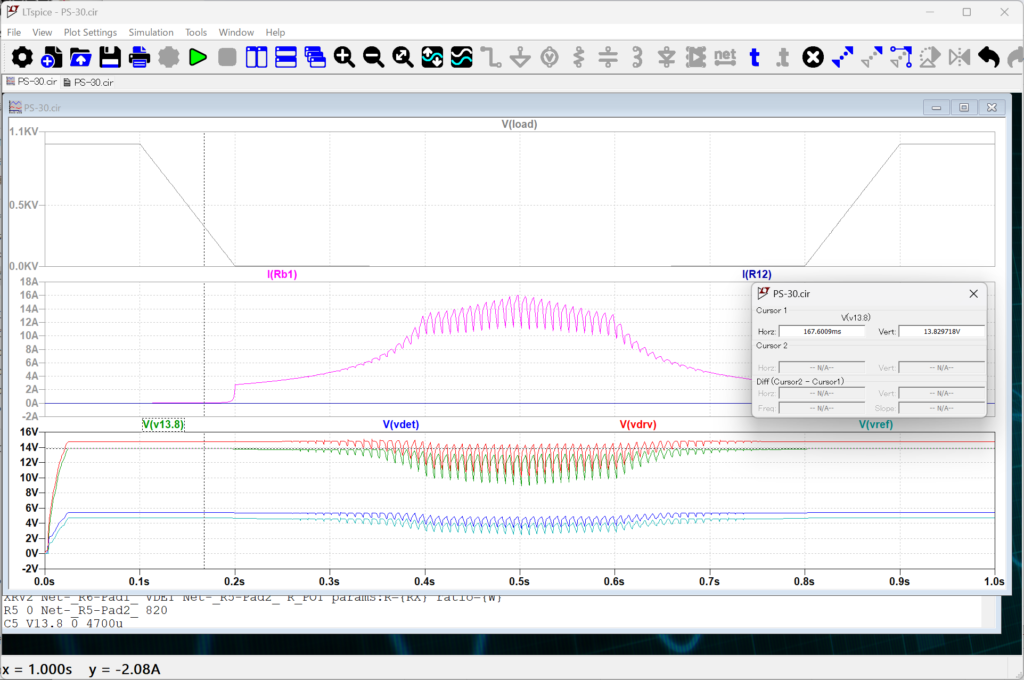

LTspiceでシミュレーションを実行し、その結果を波形で見る場合は、ノードを指定しないといけません。回路図とネットリストを突き合わせてノードを探しても良いのですが、分かりにくいので波形をみたいポイントは予め KiCad でラベルをつけておくと便利です。

シミュレーションの実行結果です。無負荷の状態では 約13.8[V]が出力されますが、負荷を約4[A]以上とるとだんだんリップルが出てくることがわかります。V(load)の値(単位無し)が負荷抵抗RB1になるので、Rb1を流れる電流I(Rb1)が負荷電流になります。

シミュレーションがうまくいって回路図をFIXしたら、次はKiCadで基板設計です。

昔は商用の高価なCAD/CAEを使わないとできなかったことが、無償のツールでできるのは本当に恵まれていますね。趣味の電子工作も一気にレベルアップできます。本当に感謝です。

なお、最近 KiCad Version 8がリリースされましたが、Version 8では この方法でネットリストをKiCadに渡して起動することができませんでした。最新のリリースでは改善されているのかも知れませんが、私はVersion 7を継続して使っています。 KiCad Version 8から LTspicepiceを使うには、KiCad-8.0からLTspiceを使う をご覧ください。